www.amlett.com, www.vbripress.com/aml, DOI: 10.5185/amlett.2016.6277

Published online by the VBRI Press in 2016

# Impact of oxygen diffusion on the performance of HfO<sub>2</sub>/GaAs metal-oxide-semiconductor field-effect-transistors

# Anindita Das<sup>1</sup>, Sanatan Chattopadhyay<sup>1, 2\*</sup>, Goutam Kumar Dalapati<sup>3</sup>

<sup>1</sup>Centre for Research in Nanoscience and Nanotechnology (CRNN), University of Calcutta, JD2 Sector-III, Saltlake, Kolkata 700098, India

Received: 05 November 2015, Revised: 22 November 2015 and Accepted: 17 December 2015

# **ABSTRACT**

In the current work, electrical performance of n-channel GaAs MOSFETs with  $HfO_2$  gate dielectrics has been investigated by considering the impact of oxygen diffusion from gate dielectric layer. Initially, the  $HfO_2$ /GaAs MOS capacitors are fabricated and its relevant process recipe has been simulated. The key parameters are extracted from both the experimental and simulated results to calibrate the simulator. The extracted parameters are subsequently fed into the simulator to investigate electrical performance of n-channel GaAs MOSFETs with varying gate lengths. The elemental diffusion of oxygen at  $HfO_2$ /GaAs interface has also been incorporated since oxygen naturally diffuses into the GaAs layer during deposition and annealing steps and thereby alters the effective doping concentration in the channel. The diffused oxygen has been observed to improve electrical performance parameters such as transconductance and threshold voltage, however, degrades DIBL of the  $HfO_2$ /GaAs MOSFET devices. Copyright © 2016 VBRI Press.

**Keywords:** GaAs; HfO<sub>2</sub>; MOSFET; threshold voltage; transconductance.

# Introduction

The Si-based complementary-metal-oxide-semiconductor (CMOS) has been the workhorse of microelectronics where successive down scaling of the technology nodes has been the preferred route for sustained performance improvement. The excellent material properties of Si, SiO<sub>2</sub> and the reliability of SiO<sub>2</sub>/Si interface have played a vital role for such four decades of progress [1]. However, such conventional scaling approach has been seriously challenged by the physics of materials and devices. The fundamental limit emerges from the aggressively scaled down ultrathin SiO2 layer where several leakage current components due to quantum-mechanical tunneling becomes unexpectedly high. Also, the state-of-the-art interconnect delay has been almost 2-order of magnitude higher than the gate delay. Consequently, it has been difficult to meet different design challenges and data communication has been identified as one of the major challenges in the progress of silicon based computation [2]. To meet such requirement, on-chip optical interconnect is emerging as a potential substitute of electrical interconnect [3-6]. Effort is being devoted to develop all-Si optical integrated circuits combining both the advantages of Si-CMOS technology and optical interconnects. However, no remarkable breakthrough has been achieved so far due to the nonavailability of suitable optical source from Si. A hybrid combination of Si-based CMOS technology and group III-V based optical source and detectors may be a solution. However, the integration of these two technologies is a real challenge and costly. In this regard, developing the gallium-arsenide (GaAs) based MOSFETs may be more advantageous over Si since it can meet both the requirements. The electron mobility of GaAs is  $\sim 6 \times 10^{-5}$  higher than Si and therefore suitable for developing highspeed switching devices [7]. Also, the GaAs based technology is well matured for developing optoelectronic devices.

The benefits of developing GaAs-based MOSFETs are well known [1, 8-15]. However, the main obstacle to fabricate GaAs-based MOSFETs is the lack of availability of high-quality gate insulators on GaAs substrates to meet the requirement for high performance switching devices. The main challenge is to reduce the mid-gap density of interface states [1]. Several reports are available where attempts have been made to grow SiO<sub>2</sub> as the gate insulator on GaAs substrate; however, these were not successful due to the lack of reliability of such insulators and the generation of an unacceptable level of interface states [16-19]. The main difficulty in growing oxides directly on GaAs substrate is the formation of Ga<sub>2</sub>O<sub>3</sub> and As<sub>2</sub>O<sub>3</sub> at the expense of surface Ga and As. The oxidation rate of Ga and

<sup>&</sup>lt;sup>2</sup>Department of Electronic Science, 92 APC Road, University of Calcutta, Kolkata 700009, India

<sup>&</sup>lt;sup>3</sup>Institute of Materials Research and Engineering, A\*STAR, (Agency for Science, Technology and Research),

<sup>3</sup> Research Link, Singapore 117602, Singapore

<sup>\*</sup>Corresponding author. E-mail: scelc@caluniv.ac.in

As is different and it leads to the creation of a significantly high density of defects and interface states. Further, the diffusion of oxygen from the gate insulator layer towards GaAs substrate in a HfO<sub>2</sub>/GaAs system becomes significant during HfO<sub>2</sub> deposition and subsequent process thermal cycles, leading to the generation of deep traps in its bandgap region and altering the effective channel doping concentration [20-24]. Consequently, the device characteristics as well as its performance parameters change significantly due to such oxygen diffusion.

The progress of atomic layer deposition (ALD) technique provides a unique opportunity to integrate high-quality gate dielectrics on GaAs [25-28]. Due to continuous effort to develop surface passivation techniques, it has been possible to create a high-quality interface with low defect density on GaAs. However, the reduction of hysteresis voltage for ALD high-k/GaAs gate stack is still challenging [25, 27, 29]. Recently, it has been shown that the development and implementation of an appropriate surface passivation step can improve interfacial quality and an interface state density as good as  $6\times10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> has been reported [30]. Also, an attempt is made to fabricate surface channel MOSFETs on epi-GaAs for achieving good interfacial quality between the oxide and GaAs [31].

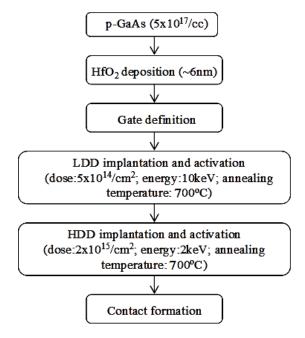

Fig. 1. Process steps simulated for fabricating the GaAs channel MOSFETs with  $HfO_2$  gate insulator.

In the current work, the impact of oxygen diffusion from  $HfO_2$  gate dielectric layer on the performance of GaAs channel MOSFETs has been studied. Initially, a process recipe for the fabrication of  $HfO_2/GaAs$  MOS capacitors has been simulated. Following the similar process flow such MOS capacitors are fabricated and characterized. The device parameters such as flat band voltage  $(V_{FB})$ , oxide thickness  $(t_{ox})$ , interface state density  $(D_{it})$ , fixed oxide charge  $(Q_F)$ , and doping concentration  $(N_A)$  are extracted from the experimental measurements and fed into device simulator for the design of state-of-the-art  $HfO_2/GaAs$  MOSFETs. A process recipe for the fabrication

of GaAs based MOSFETs by following a conventional approach has been developed and its electrical performance is obtained by simulating the structure with input data obtained from the experimental MOS capacitors.

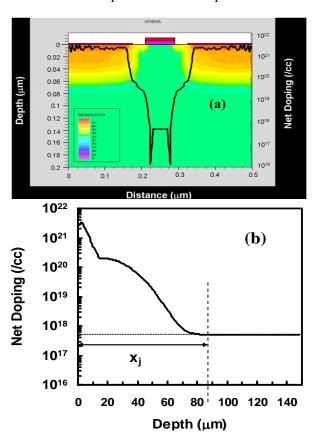

Fig. 2. (a) Simulated structure of an enhancement-mode n-channel  $HfO_2$  / GaAs MOSFET along with doping profile of the MOSFET from source to drain end; (b) doping profile of the MOSFET along the depth of the channel to substrate.

# Design and Simulation of HfO2/GaAs MOSFETs

Details of the fabrication of HfO<sub>2</sub>/GaAs MOS capacitors are described elsewhere [32]. The HfO<sub>2</sub>/GaAs MOSFETs considered in the current work have been fabricated by simulating the process recipe as has been described in **Fig. 1**.

**Fig. 2(a)** shows the simulated structure of n-channel enhancement mode GaAs MOSFET with 6 nm HfO<sub>2</sub> gate dielectric layer, fabricated by using the process simulator ATHENA, available in SILVACO [33]. Also, the doping profile of the device along the channel from source to drain at a depth of 5 nm from the HfO<sub>2</sub>/GaAs interface is overlaid. The nature of doping profile is appropriate for MOSFET operation since such doping controls the magnitude and nature of the longitudinal as well as transverse electric fields, thereby controlling its operation. The S/D doping concentration is obtained to be  $2\times10^{21}$  cm<sup>-3</sup> whereas for the channel region it is obtained to be  $5\times10^{17}$  cm<sup>-3</sup>. The maximum junction depth ( $x_j$ ) is obtained to be ~87 nm from the plot of doping profile as shown in **Fig. 2(b)**.

For simulating electrical characteristics of the device using ATLAS, the mobility degradation due to surface scattering at HfO<sub>2</sub>/GaAs interface has been considered. The Lombardi inversion layer model has been incorporated through surface roughness mobility component,  $\mu_{sr}$ , given by [33]:

$$\mu_{sr,n} = \frac{\text{DELN.CVT}}{\text{KN.CVT}} \tag{1}$$

where, the values for DELN.CVT and KN.CVT parameters are considered to be 5.82×10<sup>14</sup> V/s and 2 respectively for GaAs for the current work [33]. The field-dependent mobility has been considered to provide a smooth transition of the carrier transport from low-field to high-field, following Caughey and Thomas expression, given by [33],

$$\mu_n(E) = \mu_{n0} \left[ \frac{1}{1 + (\frac{\mu_{n0}E}{v_{com}})^{\beta_n}} \right]^{\frac{1}{\beta_n}}$$

(2)

where, E is the longitudinal electric field and  $\mu_{n0}$  is the low-field electron mobility,  $V_{satn}$  is its saturation velocity.

Phonon transitions occur in presence of traps (or defects) within the forbidden gap of the semiconductor. This is essentially a two-step process and is included into the device simulator through Shockley-Read-Hall (SRH) recombination theory [33]:

$$R_{SRH} = \frac{pn - n_{ie}^{2}}{\tau_{p0}[n + n_{ie} \exp(\frac{E_{T}}{kT_{t}})] + \tau_{n0}[p + n_{ie} \exp(\frac{E_{T}}{kT_{t}})]}$$

(3)

where,  $E_T$  is the energy difference of the traps and intrinsic Fermi level,  $T_L$  is the lattice temperature in absolute scale and  $\tau_{n0}$  and  $\tau_{p0}$  are the electron and hole lifetimes, respectively

As gate length of the MOSFET in the current work is considered to be scaled down to 20 nm, the quantum size effects are also included. The quantum size effects are modeled by solving the Schrodinger-Poisson's coupled equation along with the fundamental device equations. The solution of Schrodinger's Equation gives a quantized description of the density of states in presence of quantum mechanical confining potential variations. The calculation of the quantized density of states relies upon the solution of Schrodinger's equation [33].

$$-\frac{\hbar}{2}\frac{\partial}{\partial x}\left[\frac{1}{m_{l}}\frac{\partial\psi_{il}}{\partial x}\right] + E_{C}(x)\psi_{il} = E_{il}(x)\psi_{il}$$

(4a)

$$-\frac{\hbar}{2}\frac{\partial}{\partial x}\left[\frac{1}{m_{i}}\frac{\partial\psi_{it}}{\partial x}\right] + E_{C}(x)\psi_{it} = E_{it}(x)\psi_{it}$$

(4b)

where,  $E_{it}$  is the  $i^{th}$  bound state energy for transverse mass,  $E_{it}$  is longitudinal,  $\Psi_{it}$  is the transverse wavefunction,  $\Psi_{it}$  is the longitudinal wavefunction, and  $E_C$  is the band edge energy.

In order to study the effect of oxygen diffusion on the device performance characteristics, DIFFUSION model has been introduced and the amount of oxygen diffusion for different thermal cycles has been studied. The diffusion process can be expressed as [33]:

$$\partial_{n}C_{1} + K_{s}(C_{1} - C_{1}^{*}) = G_{1}$$

(5)

where,  $\partial_n C_I$  is the projection of the interstitial flux vector on an inward pointing unit vector normal to the boundary,  $K_S$  is the effective surface recombination rate for interstitials,  $G_I$  is the generation rate at the interface of interstitials during annealing in an oxidizing ambient, and  $C_I^*$  is the equilibrium interstitial concentration.

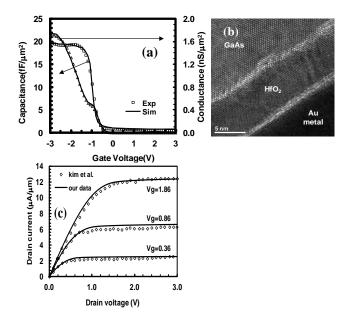

Fig. 3. (a) Experimental and simulated C-V and G-V characteristics of p-GaAs MOS capacitor with 6nm HfO $_2$  gate dielectric. (b) Cross-sectional HRTEM image of Au/ALD HfO $_2$ / GaAs stack with scale bar of 5nm. (c) Experimental and simulated  $I_D\text{--}V_D$  characteristics as a function of gate bias from depletion-mode MOSFET with  $L_g$  of 8  $\mu m$ .

**Table 1.** Summary of the parameters used in the simulation.

| Parameters                                         | Values                                       |

|----------------------------------------------------|----------------------------------------------|

| Substrate doping                                   | $5 \times 10^{17} \text{cm}^{-3}$            |

| S/D doping                                         | $2 \times 10^{21} \text{cm}^{-3}$            |

| HfO <sub>2</sub> layer thickness [32]              | 6nm                                          |

| Dielectric constant of HfO <sub>2</sub> layer [32] | 25                                           |

| Interfacial trap density at mid-gap [32]           | $\sim 10^{11} \text{cm}^{-2} \text{eV}^{-1}$ |

| Fixed oxide charge [32]                            | $\sim 10^{12} \text{ cm}^{-2}$               |

# Results and discussion

The MOS capacitors with similar specifications and material stacks have been fabricated following a standard process flow [32] and its electrical results are simulated and compared with experimental data. The plots of both experimental and simulated results are shown in Fig. 3(a) and the parameters used in the simulation are summarized in Table 1. It is apparent that the simulated results agree well with the experimental data, indicating the accuracy of the simulator as well as the models used. Thickness of the

dielectric layer was measured from the transmission electron microscopy (TEM) image of ALD HfO2 on bulk-GaAs as shown in Fig. 3(b). The TEM image shows a smooth HfO<sub>2</sub>/GaAs interface with no significant amount of defects present and also indicates the formation of a high quality gate dielectric layer of thickness 6 nm. According to the HRTEM, HfO<sub>2</sub> shows polycrystalline, which increases leakage current. It is worth to note that the interface properties and leakage current can be improved significantly by using interface passivation layer, alloy dielectric, and plasma nitridation of the dielectric [34-44]. In order to further verify accuracy of the models used, a MOSFET has been simulated using the process recipe followed by Kim et al. [9] and the output characteristics have been compared and plotted in **Fig. 3(c)**. It is observed that the simulated results are well in accord with the experimental results.

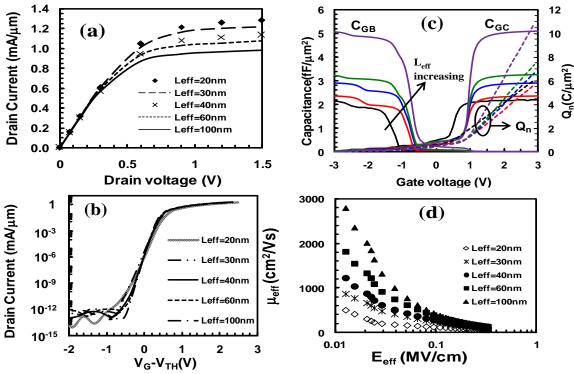

The output characteristics  $(I_D - V_D)$  of GaAs MOSFET with 6 nm HfO<sub>2</sub> gate dielectric layer with different effective channel lengths  $(L_{\rm eff})$  of 100 nm, 60 nm, 40 nm, 30 nm and 20 nm at a gate voltage of 2.2V

in current can be parameterized by a channel length modulation factor  $\lambda$  as [45, 46]:

$$I_D = I_D'(1 + \lambda V_D) \tag{6}$$

where,  $I_D$ 'is the drain current without channel length modulation. When the current is extrapolated backward from saturation region, it meets the  $V_D$ -axis (i.e.  $I_D=0$ ) at

$$V_{DS} = \frac{1}{\lambda}$$

[45]. For an ideal MOSFET,  $\lambda$  is zero and current

does not increase with increasing drain voltage after the saturation is reached. The  $\lambda$  values for the MOSFET of current consideration are extracted to be 0.067, 0.047, 0.045, 0.043, 0.04  $V^{-1}$  for  $L_{eff}$  values of 100, 60, 40, 30 and 20 nm, respectively and thereby the values imply very insignificant short-channel effect.

**Fig. 4(b)** shows the variation of drain current  $(I_D)$  with gate overdrive voltage  $(V_G - V_{TH})$  of the GaAs MOSFETs of different  $L_{eff}$  at a drain bias of 1.5V. Excellent sub-threshold characteristics are exhibited for all channel lengths and on-

Fig. 4. (a) Output characteristics for various channel lengths at gate bias of 2.2V. (b) Transfer characteristics for various channel lengths at drain bias of 1.5V. (c) Plots of variation of simulated gate-to-body ( $C_{GB}$ ) and gate-to-channel ( $C_{GC}$ ) capacitance values, keeping in mind the split C-V measurement technique. It also includes the estimated inversion charge ( $Q_n$ ) with gate bias. (d) Effective carrier mobility as a function of effective electric field

are shown in **Fig. 4(a)**. A maximum drive current of ~1.3 mA/ $\mu$ m is obtained for L<sub>eff</sub> = 20 nm and drain bias of 1.5V. This is attributed to the higher channel mobility and superior HfO<sub>2</sub>/GaAs interface as reported previously [27]. It can be seen that the drain current increases almost linearly for small biases and then it tends to saturate. However, a very close inspection to the curves shows that even in saturation region the drive current increases gradually. Such gradual increase of drive current is attributed to the channel-length modulation effect, a consequence of several short-channel effects. Such increase

state to off-state current ratio  $(I_{\text{on}}/I_{\text{off}})$  of 12 orders of magnitude is also achievable.

**Fig. 4(c)** shows the variation of estimated gate-to-body  $(C_{GB})$  and gate-to-channel  $(C_{GC})$  capacitance values and relevant inversion charge  $(Q_n)$  with gate bias. Such simulation is performed by considering the split C-V measurement technique. Once  $Q_n$  is obtained, the effective mobility can be obtained as [46]:

$$\mu_{eff} = \frac{g_d L_{eff}}{Q_n W} \tag{7}$$

where,  $g_d$  is the output conductance,  $L_{eff}$  is the effective channel length and W is the channel width.

The variation of effective mobility  $(\mu_{eff})$  with effective electric field in the channel is shown in **Fig. 4(d)**. A maximum effective mobility of 1200 cm<sup>2</sup>/Vs has been obtained which is higher than the previously reported values of 560 cm<sup>2</sup>/Vs [47], 570 cm<sup>2</sup>/Vs [48] and 970 cm<sup>2</sup>/Vs [9].

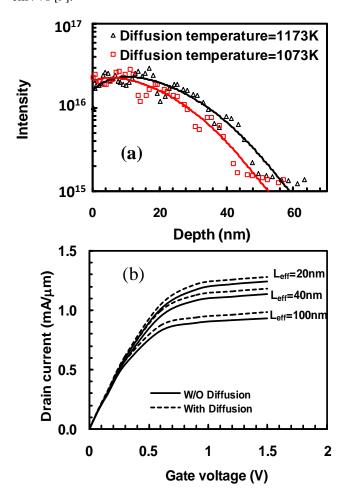

**Fig. 5.** (a) Intensity of oxygen diffusion from the HfO<sub>2</sub>/GaAs interface into the substrate for different annealing temperatures of 973K and 1073K; (b) Comparison of output characteristics with (dashed lines) and without (solid lines) the effect of oxygen diffusion.

The amount of oxygen diffusion from HfO<sub>2</sub> layer through the interface into the GaAs substrate for annealing temperatures (T<sub>anneal</sub>) of 700 °C and 800 °C, relevant for MOS processing, is shown in **Fig. 5(a)**. It is apparent that there is a significant amount of oxygen diffusion during processing and the extent of diffusion tail increases with thermal budget. Consequently, the diffused oxygen will alter the effective doping profile of the device thereby changing its electrical characteristics. **Fig. 5(b)** shows the effect of such oxygen diffusion on electrical characteristics of the MOSFETs at an annealing temperature of 1073K. The plots indicate that there is 3-5 % enhancement in drain

current in presence of diffusion. This is attributed to the fact that oxygen is an n-type dopant to GaAs and the diffused oxygen effectively increases net doping of the channel.

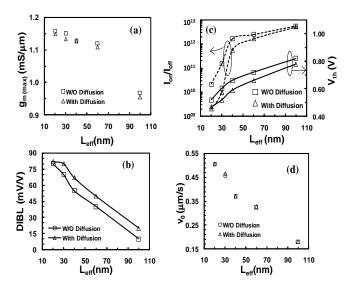

The effect of oxygen diffusion on the device performance parameters such as threshold voltage, transconductance and DIBL is shown in **Fig. 6**. The device speed  $(v_0)$  has also been calculated for MOSFETs with and without diffusion using the following expression [49];

$$v_0 = \frac{g_m}{WC} \tag{8}$$

where,  $g_m$  is transconductance, W is width of the device and C corresponds to the gate-to-channel capacitance per unit area [49].

It is observed that oxygen diffusion has adverse effects on DIBL. This is attributed to the fact that oxygen, due to its high reactivity, forms deep carrier traps in the GaAs bandgap [50]. On the other hand, improvement in transconductance and threshold voltage is observed which is due to the increase in drain current.

**Fig. 6.** (a) Transconductance; (b) DIBL; (c) Threshold voltage and current ratio; and (d) Device speed for various channel lengths with and without the effect of oxygen diffusion.

# Conclusion

The HfO<sub>2</sub>/GaAs MOS capacitors have been fabricated and characterized. A process recipe for virtually fabricating GaAs channel MOSFETs with HfO<sub>2</sub> gate dielectrics has been developed and its electrical performance is obtained by simulating the structure with input data obtained from the experimental MOS capacitors. Several parameters such as flat band voltage, oxide thickness, interface state density, fixed oxide charge, and doping concentration are extracted and fed into the simulator. The electrical characteristics have been observed. Also, the effect of oxygen diffusion, from the oxide into the substrate, on the electrical parameters has been studied. It is noted that oxygen diffusion has adverse effect on DIBL but at the same time improves transconductance and threshold voltage of the HfO<sub>2</sub>/GaAs MOSFET devices.

## Acknowledgements

A. D. likes to acknowledge the Department of Science and Technology (DST), Government of India for providing the required fund through INSPIRE Fellowship to pursue her research work.

# **Author contribution**

Conceived the plan: A.D., S.C., G.K.D.; Performed the experiments: A.D., G.K.D.; Data analysis: A.D., S.C.; Wrote the paper: A.D., S.C., G.K.D. Authors have no competing financial interests.

### Reference

- Ye, P. D.; Wilk, G. D.; Kwo, J.; Yang, B.; Gossmann H. J-L, Frei, M.; Chu, S. N. G.; Mannaerts, J. P.; Sergent, M.; Hong, M.; Ng, K. K.; Bude, J.; *IEEE Electron Device Letters*, 2003, 24(4), 209. DOI: 10.1109/LED.2003.812144

- Haurylau, M.; Chen, G.; Chen, H.; Zhang, J.; Nelson, N. A.; Albonesi, D. H.; Friedman, E. G.; Fauchet, P. M.; *IEEE J. Sel. Top. Quantum Electronics*, 2006, 12, 1699.

DOI: 10.1109/JSTQE.2006.880615

- He, G.; Sun, Z. (Eds.); High-k Gate Dielectrics for CMOS Technology, Wiley-VCH 2012.

DOI: 10.1002/9783527646340

- Chen, G.; Chenb, H.; Haurylaua, M.; Nelson, N. A.; Albonesic, D. H.; Fauchet, P. M.; Friedman, E. G.; *Integration, the VLSI Journal*, 2007, 40, 434.

DOI: 10.1016/j.vlsi.2006.10.001

- Havemann, R. H.; Hutchby, J. A.; Proceedings of the IEEE, 2001, 89, 586.

**DOI:** 10.1109/5.929646

- Oktyabrsky ,S.; Castracane, J.; Kaloyeros, A. E.; Symposium on Integrated Optoelectronic Devices. International Society for Optics and Photonics, Vol. 213 2002.

- Hong, M. W.; Kwo, J.; Kortan, A. R.; Mannaerts, J. P.; Sergent, A. M.; Science, 1999, 283, 1897.

DOI:10.1126/science.283.5409.1897

- Wu, J. Y.; Wang, H. H.; Wang, Y. H.; Houng, M. P.; *IEEE Electron Device Lett.*, 1999, 20, 18.

DOI: 10.1109/55.737560

- Kim, H.; Ok, I.; Zhang, M.; Lee, T.; Zhu, F.; Yu, L.; Lee, Jack C.; *Appl. Phys. Lett.*, **2006**, 89, 222904.

DOI:10.1063/1.2396914

- Kim, H.; Ok, I.; Zhang, M.; Zhu, F.; Park, S.; Yum, J., Zhao, H.;

Lee, Jack C.; Appl. Phys. Lett., 2008, 92, 032907.

DOI: 10.1063/1.2838294

- Hill, R. J. W.; Moran, D.A.J.; Xu Li; Haiping Zhou; Macintyre, D.; Thoms, S.; Asenov, A.; Zurcher, P.; Rajagopalan, K.; Abrokwah, J.; Droopad, Ravi; Passlack, M.; Thayne, I.G.; *IEEE Electron Device Lett.*, 2007, 28,1080.

DOI: 10.1109/LED.2007.910009

- Ok, I.; Kim, H.; Zhang, M.; Zhu, F.; Park, S.; Yuma, J.; Zhao, H.; Lee, Jack C.; *Microelectron. Eng.*, 2009, 86, 291. DOI:10.1016/j.mee.2008.09.017

- Rajagopalan, K.; Abrokwah, J.; Droopad, Ravi; Passlack, M.; *IEEE Electron Devices Lett.*, 2006, 27, 959.

DOI: 10.1109/LED.2006.886319

- Ok, I.; Kim, H.; Zhang, M.; Lee, T.; Zhu, F.; Yu, L.; Koveshnikov, S.; Tsai, W.; Tokranov, Yakimov, V.; M.; Oktyabrsky, S.; . Lee, Jack C; IEDM Tech. Dig., Vol.829 2006.

- Rajagopalan, K.; Droopad, R.; Abrokwah, J.; Zurcher, P.; Fejes, P.; Passlack, M.; *IEEE Electron Devices Lett.*, 2007, 28, 100. DOI:10.1109/LED.2006.889502

- 16. Houng, M.P.; Wang, Y.H.; Huang, C.J.; Huang, S.P.; Horng, J.-H.; Solid-State Electronics, 2000, 44, 1917.

**DOI:** <u>10.1016/S0038-1101(00)00178-7</u>

- Huang, C.; Ya, Z.; Horng, J.; Houng, M.; Wang, Y.; Jpn. J. Appl. Phys., 2002, 41, 5561.

DOI: 10.1143/JJAP.41.5561

- Liu, C.H.; Lin, T.K.; Chang, S.J.; Solid-State Electronics, 2005, 49, 1077.

**DOI:** <u>10.1016/j.sse.2005.05.006</u>

- Lee, H.; Lin, Y.; Semicond. Sci. Technol., 2010, 25, 015005.

DOI: 10.1088/0268-1242/25/1/015005

- 20. Sturge, M. D.; *Phys. Rev.*, **1962**, *127*, 768. **DOI:** <u>10.1103/PhysRev.127.768</u>

Zhu, X.; Zhu, Li, J-m; A.; Liu, Z.; Ming, N., J. Mater. Sci. Technol., 2009, 25, 289.

**DOI:** www.jmst.org/EN/Y2009/V25/I03/289

Lin, A. L.; Omelianovski, E.; Bube, R. H.; J. Appl. Phys., 1976, 47, 1852.

**DOI:** <u>10.1063/1.322904</u>

- Lagowski, J.; Lin, D.G.; Aoyama, T.; Gatos, H. C.; Appl. Phys. Lett., 1984, 44, 336.

DOI: 10.1063/1.94751

- Hata, M.; Takata, H.; Yano, T.; Fukuhara, N.; Maeda, T.; Uemura, Y.; J. Cryst. Growth, 1992, 124, 427.

DOI: 10.1016/0022-0248(92)90495-5

- Dalapati, G. K.; Tong, Y.; Loh, W. Y.; Mun, H. K.; Cho, B. J.;

IEEE Trans. Elect. Dev., 2007, 54, 1831.

DOI: 10.1109/TED.2007.901261

- Xuan, Y.; Wu, Y. Q.; Lin, H. C.; Shen, T.; Ye, P. D.; *IEEE Elect. Dev. Lett.*, 2007, 28, 935.

DOI: 10.1109/LED.2007.906436

- Dalapati, G. K.; Kumar, M. K.; Chia, C. K.; Gao, H.; Wang, B. Z.; Wong, A. S. W.; Kumar, A.; Chiam, S. Y.; Pan, J. S.; Chi, D. Z.; *J. Electrochem. Soc.*, 2010, 157, H825.

DOI: 10.1149/1.3453935

- Dalapati, G. K.; Wong, T. K. S.; Li, Y.; Chia, C. K.; Das, A.; Mahata, C.; Gao, H.; Chattopadhyay, S.; Kumar, M. K.; Seng, H. L.; Maiti, C. K.; Chi, D. Z.; Nanoscale Res. Lett., 2012, 7, 99.

DOI: http://www.nanoscalereslett.com/content/7/1/99

- Lee, H. D.; Feng, T.; Yu, L.; Mastrogiovanni, D.; Wan, A.; Gustafsson, T.; Garfunkel, E.; Appl Phys Lett, 2009, 94, 222108.

DOI: 10.1063/1.3148723

- Dalapati, G. K.; Chia, C. K.; Tan, C. C.; Tan, H. R.; Chiam, S. Y.;

Dong, J. R.; Dong, Das, A.; Chattopadhyay, S.; Mahata, C.; Maiti,

C. K.; Chi, D. Z.; ACS Appl. Mater. Interfaces, 2013, 5, 949.

DOI: 10.1021/am302537b

- Hackley, J. C.; Demaree, J. D.; Gougousi, T.; *Appl. Phys. Lett.*, **2008**, 92, 162902.

DOI: 10.1063/1.2908223

- Das ,A.; Chattopadhyay ,S.; Dalapati, G. K.; Chi ,D. Z.; Kumar,M. K.; Proc. SPIE, 16th International Workshop on Physics of Semiconductor Devices, Vol. 8549, 85493I 2012.

- SILVACO\_Inc., Atlas and Athena User's Manual, Santa Clara, CA, 2003.

- Dalapati, G. K.; Tong. Y.; Loh, W. Y.; Mun, H. K.; Cho, B. J.; *Appl. Phys. Lett.* 2007, 90, 183510.

DOI: 10.1063/1.2732821

- Mahata, C.; Mallik, S.; Das, T.; Maiti, C. K.; Dalapati, G. K.; Tan, C. C.; Chia, C. K.; Gao, H.; Kumar, M. K.; Chiam, S. Y.; Tan, H. R.; Seng,, H. L.; Chi, D. Z.; Miranda, E.; Appl. Phys. Lett. 2012, 100, 062905.

DOI: 10.1063/1.3684803

Dalapati, G. K.; Sridhara, A.; Wong, A. S. W.; Chia, C. K.; Lee, S. J.; Chi, D. Z.; Appl. Phys. Lett. 2007, 91, 242101.

DOI: 10.1063/1.2822422

- Dalapati, G. K.; Sridhara, A.; Wong, A. S. W.; Chia, C. K.; Lee, S. J.; Chi, D. Z.; *J. Appl. Phys.* 2008, 103, 034508.

DOI: 10.1063/1.2840132

- Dalapati, G. K.; Oh, H. J.; Lee, S. J.; Sridhara, A.; Wong, A. S. W.; Chi, D. Z.; Appl. Phys. Lett. 2008, 92, 042120.

DOI: 10.1063/1.2839406

- Dalapati, G. K.; Sridhara, A.; Wong, A. S. W.; Chia, C. K.; Chi, D. Z.; Appl. Phys. Lett. 2009, 94, 073502.

DOI: 10.1063/1.3079409

- Dalapati, G. K.; Sridhara, A.; Wong, A. S. W.; Chia, C. K.; Chi, D. Z.; ECS Trans. 2008, 16, 387.

DOI: 10.1149/1.2981620

- Das, T.; Mahata, C.; Maiti, C. K.; Dalapati, G. K.; Chia, C. K.; Chi, D. Z.; Chiam, S. Y.; Seng., H. L.; Tan, C. C.; Hui, H. K.; Sutradhar, G.; Bose, P. K.; *J. Electrochem. Soc.* 2012, *159*, G15.

DOI: 10.1149/2.072202jes

- Mukherjee, C.; Das, T.; Mahata, C.; Maiti, C. K.; Chia, C. K.; Chiam, S. Y.; Chi, D. Z.; Dalapati, G. K.; ACS Appl. Mater. Interfaces, 2014, 6, 3263.

DOI: 10.1021/am405019d

- Dalapati, G. K.; Chia, C. K.; Mahata, C.; Krishnamoorthy, S.; Tan, C. C.; Tan, H. R.; Maiti, C. K.; Chi, D. Z.; *IEEE Trans. Electron. Dev.* 2013, 60,192.

**DOI:** <u>10.1109/TED.2012.2226243</u>

- Dalapati, G. K.; Chakraborty, S.; Mahata, C.; Bhuiyan, M. A.; Dong,

J.; Iskander, A.; Masudy-panah, S.; Dinda, S.; Yang, R. B.; Lee, T.;

Chi, D. Z.; Chia, C. K.; *Mater. Lett.* 2015, 156, 105.

DOI:10.1016/j.matlet.2015.05.001

- Ye, P. D.; Wilk, G. D.; Yang, B.; Kwo, J.; Gossmann, H.-J. L.; Hong, M.; Ng, K. K.; Bude, J.; Appl. Phys. Lett., 2004, 84, 434.

DOI: 10.1063/1.1641527

- Schroder, D. K.; Semiconductor Material and Device Characterization, 3<sup>rd</sup> Edition, IEEE Press and Wiley-Interscience, 2006.

**ISBN:** 978-0-471-73906-7

- Ok, I.; Kim, H.; Zhang, M.; Lee, T.; Zhu, F.; Thareja, G.; Yu,L.; Koveshnikov, S.; Tsai, W.; Tokranov, V.; Yakimov, M.; Oktyabrsky, S.; Lee, J.; 64th Device Research Conference Digest 2006

- Arora, N.; MOSFET Models for VLSI Circuit Simulation Springer, Vienna 107 1993.

- 49. O'Neill, A.G.; Antoniadis, D.A.; IEEE Trans. Elect. Dev., 1996, 43, 911

**DOI:** <u>10.1109/16.502123</u>

50. Taguchi, A.; Kageshima, H.; Phys. Rev. B, 1999, 60 5383.

**DOI:** <u>10.1103/PhysRevB.60.5383</u>

field of materials science and technology particularly in the area of structure, synthesis and processing, characterisation, advanced-state properties and applications of materials. All published articles are indexed in various databases and are available download for free. The manuscript management system is completely electronic and has fast and fair peer-review process. The journal includes review article, research article, notes, letter

to editor and short communications.